Въпреки че тази година TSMC започна производство на 7-нанометрови чипове, а по-късно същото ще направи и Samsung, използването на „по-тънкия” технологичен процес не е рентабилно за всички блокове в чипа, поради което водещите играчи в индустрията търсят други, по-ефективни решения.

Несъмнено, графичните и централните процесори изискват най-модерния технологичен процес. Периферията, от друга страна, под формата на интерфейси, памет и всички видове ускорители/копроцесори не е длъжна да следва същото правило. За тези блокове са достатъчни 16 нм, 22 нм и дори по-стари технологични процеси. Но как да се съчетае всичко това в един чип?

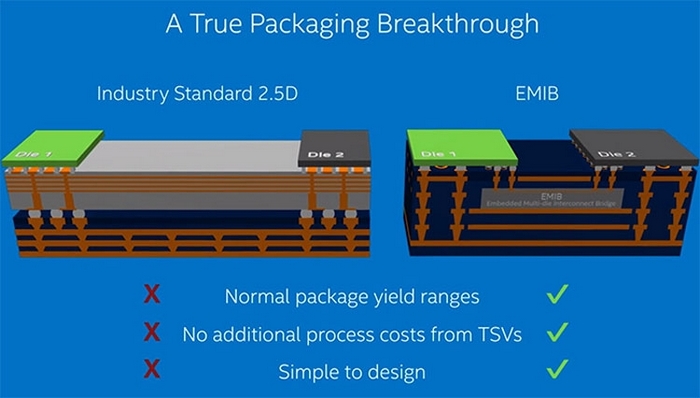

Започвайки с Fiji GPU, AMD с лека ръка въведе графичните процесори в пакет 2.5D. Но тук има един проблем: доста скъпо и сложно е производството на силициевия мост-подложка с TSVs съединения с изключително малък диаметър – десет пъти по-малък, отколкото при обикновените канали с вертикални метализация.

По-достъпна алтернатива предлага Intel – това е EMIB пакетът. Вместо голям мост, няколко силициеви кристали се комбинират в едно хибридно решение, като се използват серии от малки мостове с проста структура и без TSV. Накрая, всичко се залива с компаунд (смес). Оказва се, че подобно решение е по-просто и по-евтино.

На конференцията Hot Chips 2018 за втора поредна година Intel демонстрира практическата зрялост на технологията EMIB. В такава опаковка е произведен хибриден процесор с Core CPU, Vega GPU и памет HBM. Но компанията планира да отиде по-далеч, създавайки още по-компактни решения, които ще комбинират, например, 10-нанометров процесор с 14- и 22-нанометрови интерфейси и контролери.

Тази концепция се развива под името „чиплети” (chiplets). Конкуреннът AMD също разработва чиплети, с уточнението, че пакетите за тях ще се произвеждат от GlobalFoundries или TSMC.

Индустрията със сигурност се движи към „многокристални чипове”. По друг начин е малко вероятно да бъде удължен прословутият закон на Мур, следването на който е все по-трудно напоследък от Intel и останалите чипмейкъри. Индустрията е изправена пред предизвикателството да продължи да увеличава функционалността на чиповете, при условие, че вече е достигната граничната тактова честота.